# Lithiumate™ **EL01**

### Li-Ion BMS cell-board processor

#### **Features**

- Forms the core of a Li-lon BMS cell board, mounted on cells

- Powered by the cell, with very low current draw (~ 2 µA in standby)

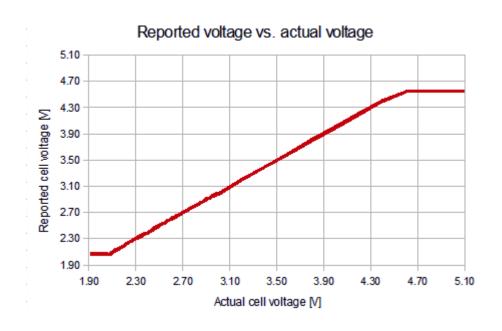

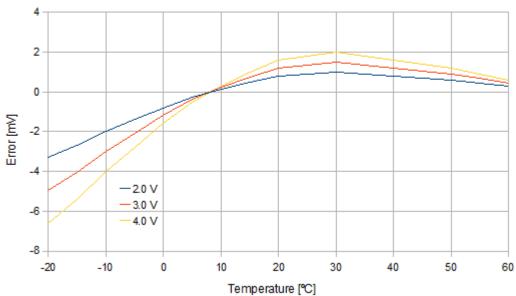

- Measures the voltage of a single Li-lon cell or a set of cells in parallel (1.9 to 4.5 V, +/- 15 mV)

- Measures the temperature of its cell board

- Drives a load to balances the cells

- Communicates to adjacent cellboards through a 1-wire digital interface

- Communication with BMS controller is typically through a 2wire, isolated bus

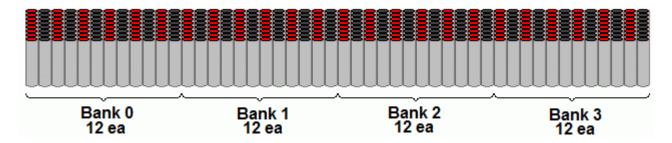

- Stackable, for up to 16 cells in series in a single bank, up to 255 cells in series with multiple banks

### **Description**

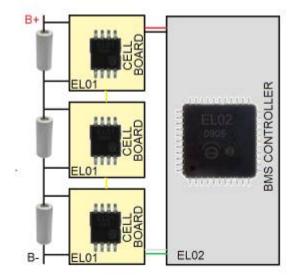

The EL01 is a programmed microcontroller that forms the core of an Elithion BMS cell board circuit. Each circuit monitors the voltage and temperature of a Li-lon cell and passes that information to the following circuit through a 1-wire interface. The first circuit in a bank receives communication from a BMS controller (using an Elithion EL2 IC) and the last circuit in the bank transmits communications back to the BMS controller

## **Applications**

- Vehicle traction packs

- Li-Ion UPS batteries

- Large Li-Ion battery packs

### **Typical application**

A BMS consists of one BMS controller (using an EL02) and cell-boards for between 1 and 255 cells in series, with one EL01 for each cell in series.

## **Absolute maximum ratings**

| Vdd supply voltage<br>Port voltage, neg                                                                                                                                                         | 7.0<br>-0.3                                    | V<br>V                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------|

| Port voltage, pos Total power dissipation Vss out current Vdd in current Port clamp current Port sink current Port source current Total port sink current Total port source current Temperature | Vdd+0.3 700 200 150 ±20 25 25 100 100 -40°C to | V<br>mW<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>+85°C |

| remperature                                                                                                                                                                                     | -40°C to                                       | +85°C                                                |

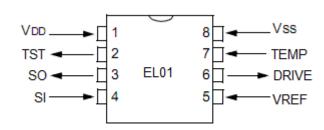

## Pin-out

## **Ordering**

| Format        | Part number | Package | Temper. range  | Order qty |

|---------------|-------------|---------|----------------|-----------|

| Tape and reel | EL01TR      | 8MSOP   | -40°C to +85°C | 3300      |

| Cut tape      | EL01CT      | 8MSOP   | -40°C to +85°C | Any       |

| Tube          | EL01TU      | 8MSOP   | -40°C to +85°C | 100       |

## **Electrical characteristics**

Unless otherwise noted, 3.0 Vdc, 25 °C.

| Symbol                | Parameter                            | Conditions                                           | Min  | Nom     | Max  | Units |

|-----------------------|--------------------------------------|------------------------------------------------------|------|---------|------|-------|

| V <sub>supply</sub>   | Supply voltage                       |                                                      | 1.9  |         | 5.0  | V     |

| V <sub>range</sub>    | Cell voltage sensing range           |                                                      | 2.09 |         | 4.54 | V     |

| V <sub>resol</sub>    | Cell voltage sensing resolution      |                                                      |      | 10      |      | mV    |

| V <sub>accur</sub>    | Cell voltage sensing accuracy        | Within V <sub>range</sub>                            |      | ±10     | ±15  | mV    |

| V <sub>temp-err</sub> | Cell voltage sensing error over temp | Within V <sub>range</sub> -20 to +60°C               |      | +2 / -7 | ±18  | mV    |

|                       |                                      | Within V <sub>range</sub> Charging range: 0 to +60°C |      | ±2      | ±17  | mV    |

| I <sub>sply</sub>     | Cell drain current                   | Stand-by                                             |      |         | 2    | μA    |

|                       |                                      | Active,<br>1-reading / sec                           |      | 1.5     | 2.0  | mA    |

| T <sub>range</sub>    | Temperature sensing range            |                                                      | -99  |         | +99  | °C    |

| T <sub>accur</sub>    | Temperature sensing accuracy         |                                                      |      | ±2      |      | °C    |

| F <sub>comm</sub>     | Communication rate                   |                                                      |      | 5       |      | kBaud |

## **Pin functions**

| Pin | Name  | Direction | Function                                   |

|-----|-------|-----------|--------------------------------------------|

| 1   | VDD   | Power     | Positive supply                            |

| 2   | TST   | Out       | Test output                                |

| 3   | DO    | Out       | Communication to the next cell board       |

| 4   | DI    | In        | Communication from the previous cell board |

| 5   | VREF  | In        | Voltage reference                          |

| 6   | TEMP  | In        | Temperature sensing                        |

| 7   | DRIVE | Out       | Balance load drive                         |

| 8   | VSS   | Power     | Supply common                              |

## **Theory of operation**

[Only available to qualified Elithion clients.]

### **Application information**

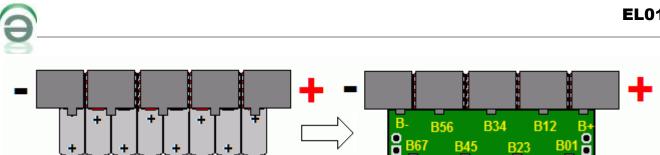

#### **Banks**

The Elithion BMS can handle up to 256 cells in series. For technical reasons, and for increased reliability, the cells in series are subdivided into groups, called "banks".

A Bank is a set of cells wired in series that communicates with the controller through its own communication cable.

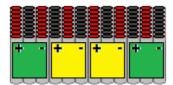

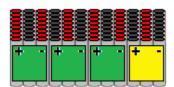

#### Positive End, mid-bank and negative end circuits

Cell board circuits come in 3 flavors:

- Positive end:

- the circuit connected to the the positive cell in a bank

- each bank has one positive end circuit

- it receives data from the BMS controller (typically through a 2-wire, isolated link)

- it transmits data to the more negative adjacent circuit, through a 1-wire link

#### Mid-bank:

- a circuit connected to any cell that is neither the most positive nor the most negative of a bank

- the number of mid-bank circuits in a bank ranges from 0 (only 2 cells in a bank) to about 14 (16 cells in a bank)

- it receives data from the more positive adjacent circuit, through a 1-wire link

- it transmits data to the more negative adjacent circuit, through a 1-wire link

- Negaitive end:

- the circuit connected to the the positive cell in a bank

- each bank has one negative end circuit

- it receives data from the more positive adjacent circuit, through a 1-wire link

- it sends data to the BMS controller (typically through a 2-wire, isolated link)

#### Cell boards

A cell board is mounted directly on the cell(s) it monitors, to measure its (their) voltage. It also measures its own temperature, which is indirectly related to the cell temperature.

A cell board may include 1 or more cell board circuits on it; in some cases, an entire bank may be implemented on a single cell board.

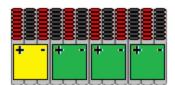

• Single cell boards are best for large cells, such as prismatic cells

Multiple cell boards are best for blocks of small cells. They have the advantage of requiring far fewer connections, as a single pad handles the connection between 2 cells, and the 1-wire link between cell board circuits is implemented on the PCB.

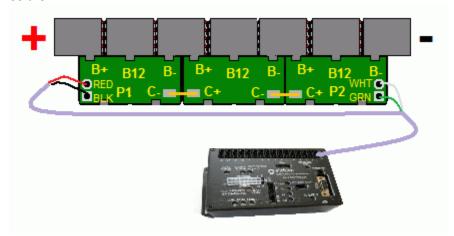

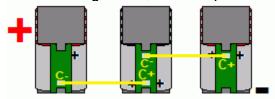

#### Intra-bank communications

Adjacent cell board circuits communicate digital data through a single-wire serial communication link which is not isolated and non-differential. The two ends of the link are labeled "C-" (on the more positive of the two circuits) and "C+" (on the more negative). When two adjacent circuits are physically located on separate PCB assemblies, the routing and length of this wire are critical, as it may pick-up noise generated by the system (typically a charger or a motor controller). Excessive noise will disrupt communications. To avoid that, the wire must be as short as possible, or at least routed in parallel with the corresponding current carrying conductor (such as a power cable) yet not be wrapped around it.

If those measures are not sufficient, a shielded wire may be used, with the shield connected to the B- pad of the more positive of the two cell circuits.

Finally, if all these measures are not sufficient, it may be necessary to split the bank at that point into two separate banks, and use two end circuits instead of two mid-bank circuits.

#### Bank to BMS controller communications

The BMS controller transmits digital data to the most positive circuit in a bank, and it receives data in return from the most negative circuit in that bank. The format is identical to the one of the intra-bank communication. But this link is different in that it typically requires electrical isolation, and it typically needs to be physically longer. For that reason, use of a 2-wire differential link through an opto-isolator is suggested. On the positive end of a bank, a 2-wire link from the BMS controller drives an opto-isolator, which in turn drives the "C+" input of the positive end circuit. On the negative end of that bank, the "C-" output of the negative end circuit drives another opto-isolator, which in turn drives a 2-wire link to the BMS controller.

#### Balancing

A well balanced battery pack (meaning that all its cells start at the same State Of Charge) is able to deliver the maximum charge to its load. That is because the cell with the lowest capacity (its limiting factor) is used fully, as it is both the first one to reach full charge and the first one to reach full discharge.

A battery pack may be well balanced at the time of manufacture; yet, such a pack will become imbalanced over time due to the difference in its cells' leakages (self-discharge) currents. The result is that the various cells will have differing SOCs, and, before the cell with the lowest capacity has a chance to be fully charged, charging must cease because some other cell has reached its full charge.

With some other battery chemistries, balancing can be accomplished with an equalization

phase, during which the most charged cells are overcharged and dissipate the extra energy as heat. That is not possible with Li-lon cells, as they would keep on charging, reaching dangerous voltage levels.

Balancing of a Li-lon battery pack is accomplished by removing extra energy in the most charged cells, to allow a bulk charger to charge the remaining cells. The extra energy can be dissipated as heat (passive balancing) or transferred to other cells (active balancing). Alternatively, balancing may be done by transferring additional energy to the least charged cells (which is another form of active balancing). In smaller batteries, it is also possible to use small, multiple chargers to charge each cell in series individually, to achieve the same effect.

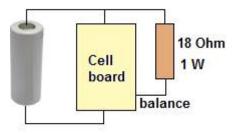

#### Passive balance

Because Li-lon cells typically have a very low leakage (self-discharge current) current, balancing can be implemented very simply, by dissipating energy in a resistors. In most applications, a logic level MOSFET driving an 18 Ohm, 1W resistor will provide sufficient passive balance. For example, such a load will provide a balance current of 200 mA for a fully charged LiFePO4 cell, and 230 mA for a LiPo cell. For very large packs (> 1000 Ah), or packs with a very short charging time (< 1% of the time) that may not be sufficient, and a large load will be required.

#### Active balance

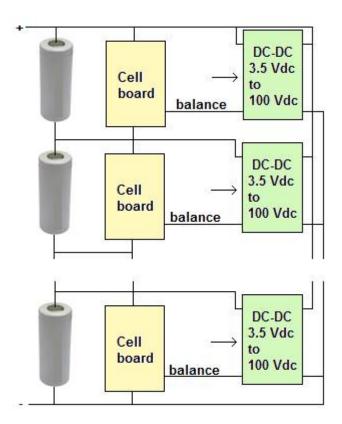

The cost, complexity and space requirement of an active balance circuit can hardly be justified in Li-Ion batteries (unlike for Lead Acid batteries, which have a much higher leakage current). Still, in rare applications, active balancing is a requirement.

To implement active balancing, the balance resistor is replaced with a DC-DC converter, whose output is connected to the entire pack (or just a portion of it). When the BMS turns on balancing for a particular cell, the DC-DC input converter is powered, and the cell's excess charge is transferred to the entire pack.

#### **LED**

An LED (with a current limiting resistor) may be added in parallel with the balance resistor, to provide visual indication of the circuit's operation:

- One blink each time the voltage is read

- Steady on while balancing

- Two blinks, repeated 3 times, when first connected to a cell

### **Suggested circuits**

### [Only available to qualified Elithion clients.]

#### **BOMs**

These Bill Of Materials are representative. They are useful for a cost analysis, but they are not the actual BOM.

#### Mid-bank circuit:

| 1 | EL01               | Cell board IC, rev 1.03 |  |  |

|---|--------------------|-------------------------|--|--|

| 1 | Cell board         | REV A                   |  |  |

| 2 | 10n                | 50V X7R MONO 0603       |  |  |

| 1 | 500 Ohm @ 100 MHz  | ferrite 0805            |  |  |

| 1 | Red                | 0805 SMD                |  |  |

| 5 | 1.0K               | 5% 1/10W 0603           |  |  |

| 1 | 18                 | 5% 1W 2512              |  |  |

| 1 | 25K @ 25 °C NTC    | 180 mW 5% 0603          |  |  |

| 1 | ADR5044ARTZ        | 4.096V 0.2% VREF SC70   |  |  |

| 1 | MMBF170            | N-MOS 60V 500mA SOT23   |  |  |

| 1 | MBT3904 NPN, SOT23 |                         |  |  |

### Additional components for an end board:

| 1 | PS2701-1 | Opto-isolator |  |

|---|----------|---------------|--|

| 2 | 1.0K     | 5% 1/10W 0603 |  |

| 1 | MMBT3906 | PNP, SOT23    |  |

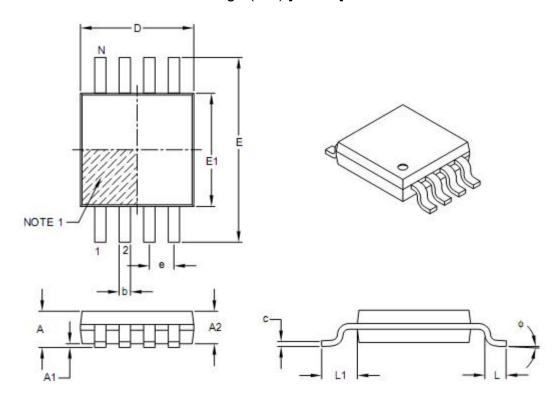

## **Packaging information**

8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

| U                        | INITS: mm | MIN      | NOM  | MAX  |

|--------------------------|-----------|----------|------|------|

| Number of Pins           | N         |          | 8    |      |

| Pitch                    | е         | 0.65 BSC |      |      |

| Overall Height           | А         | -        | -    | 1.10 |

| Molded Package Thickness | A2        | 0.75     | 0.85 | 0.95 |

| Standoff                 | A1        | 0.00     | -    | 0.15 |

| Overall Width            | E         | 4.90 BSC |      |      |

| Molded Package Width     | E1        | 3.00 BSC |      |      |

| Overall Length           | D         | 3.00 BSC |      |      |

| Foot Length              | L         | 0.40     | 0.60 | 0.80 |

| Footprint                | L1        | 0.95 REF |      |      |

| Foot Angle               | φ         | 0°       | -    | 8°   |

| Lead Thickness           | С         | 0.08     | -    | 0.23 |

| Lead Width               | b         | 0.22     | -    | 0.40 |

- Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions which shall not exceed 0.15 mm per side.

Dimensioning and tolerances per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

## **Sales and support**

Elithion LLC

393 Iris Ave Boulder CO 80301 USA

1-303-413-1500

support@liionbms.com

elithion.com